Abstract

Abstract

AI-based applications are being adopted faster than any other new technology in history. This results in extreme demand for compute to support inference at scale. As if that was not challenging enough, AI model architectures evolve at a breakneck pace, requiring systems infrastructure to support them with high velocity. The goal of AI compilers is to make AI workloads run efficiently in the underlying hardware with as little manual work as possible — at their heart is the use of AI techniques themselves. In this talk, I will talk about the origins and history of AI compilers, the current state of the art, and how AI-based codegen is pointing to a likely revolution in AI system software. I will end with thoughts about implications for computer systems architecture and HW-SW co-design.

Bio

Luis Ceze is Lazowska Professor in the Paul G. Allen School of Computer Science and Engineering at the University of Washington, where he has been on the faculty since 2007. He is also VP of AI Systems Software at NVIDIA, following the acquisition of OctoAI, where he was co-founder and CEO. His current research focuses on scalable and efficient AI systems, as well as the intersection of computing and biology for IT applications. He is part of the UW SyFI (Systems for Future Intelligence lab), and the UW MISL (Molecular Information Systems Lab). He is a Sloan Research Fellow and ACM Fellow.

Abstract

Abstract

This talk will critically examine various aspects of computing system design and the research & development process that goes into it, from the speaker’s perspective. We aim to deconstruct some assumptions that go into various design, research, and development processes, with the goal of enabling and hopefully inspiring better and fundamentally more efficient ways of doing things. A key assumption we will deconstruct is the processor-centric design mindset and paradigm of thinking about and designing computing systems, which is hitting many scaling limits. We aim to also examine other issues, including how we analyze and vet scientific research and its broader implications.

Bio

Onur Mutlu is a Professor of Computer Science at ETH Zurich. He previously held the William D. and Nancy W. Strecker Early Career Professorship at Carnegie Mellon University. His research interests are in computer architecture, computing systems, hardware security, memory & storage systems, and bioinformatics, with a major focus on designing fundamentally energy-efficient, high-performance, and robust computing systems. Many techniques he, with his group and collaborators, has invented over the years have largely influenced industry and have been widely employed in commercial microprocessors and memory & storage systems used daily by billions of people. He obtained his PhD and MS in ECE from the University of Texas at Austin and BS degrees in Computer Engineering and Psychology from the University of Michigan, Ann Arbor. He started the Computer Architecture Group at Microsoft Research (2006-2009), and held product, research and visiting positions at Intel Corporation, Advanced Micro Devices, VMware, Google, and Stanford University. He received various honors for his impactful research, including the 2025 IEEE Computer Society Harry H. Goode Memorial Award “for seminal contributions to computer architecture research and practice, especially in memory systems,” 2024 IFIP Jean-Claude Laprie Award in Dependable Computing (for the original RowHammer work), 2021 IEEE High Performance Computer Architecture Conference Test of Time Award (for the Runahead Execution work), 2022 Persistent Impact Prize of the Non-Volatile Memory Systems Workshop (for the leading architectural work on Phase Change Memory), 2025 Dependable Systems and Networks Conference Test of Time Award, 2023 Huawei OlympusMons Award in Storage Systems, 2019 ACM SIGARCH Maurice Wilkes Award, and dozens of best paper or “Top Pick” paper recognitions at various leading computer systems, architecture, and security venues. He is an ACM Fellow, IEEE Fellow, and an elected member of the Academy of Europe. He enjoys teaching, mentoring, and enabling broad global access to high-quality research and education. He has supervised 24 PhD graduates, many of whom received major dissertation & other awards, 15 postdoctoral trainees, and more than 60 Master’s and Bachelor’s students. His computer architecture and digital logic design course lectures and materials are freely available on YouTube (also here), and his research group makes a wide variety of open-source artifacts freely available online. For more information, please see his webpage at https://people.inf.ethz.ch/omutlu/.

Moderator: Gabriel Loh, AMD Research

Description

The research community is already focused on the "big" bottlenecks and challenges for AI, such as TOPS, power, memory bandwidth and capacity, TCO, etc. However, as AI systems continue to scale, other (perhaps less obvious) challenges and issues could significantly stifle the widespread and positive impactful usage of AI across society. Our esteemed panelists will share their thoughts and perspectives on these lurking "AI Demons." This panel will provide discussion and debate, along with audience Q&A, that aims to share insights and help guide the research agenda for the MICRO community.

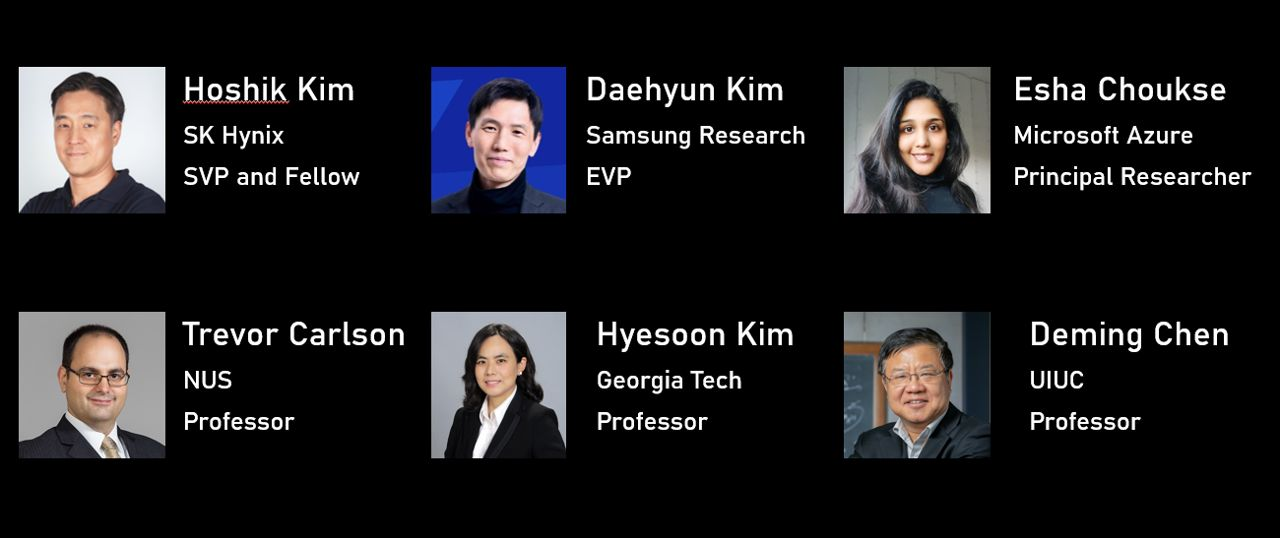

Panelists