#### Warped-GATES

Gating Aware Scheduling and Power Gating for GPGPUs Mohammad Abdel-Majeed, Daniel Wong and Murali Annavaram University of Southern California

University of Southern California

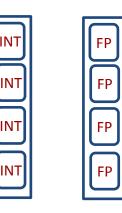

- Scheduler greedily issues ready instructions

- Agnostic to instruction type.

- Scheduler greedily issues ready instructions

- Agnostic to instruction type.

- Scheduler greedily issues ready instructions

- Agnostic to instruction type.

- Scheduler greedily issues ready instructions

- Agnostic to instruction type.

- Scheduler greedily issues ready instructions

- Agnostic to instruction type.

# **Proposed Techniques**

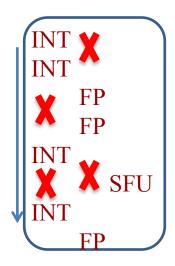

- Gating Aware Scheduler (GATES)

- Gives priority to same instruction type during scheduling.

- Is able to increase the length of the idle periods.

- Idle periods are not long enough to avoid negative savings!!

- Blackout technique

- Eliminates negative savings by forcing the unit to stay in power gating state.