# SMARQ: Software-Managed Alias Register Queue for Dynamic Optimizations

Cheng Wang, Youfeng Wu, Hongbo Rong, Hyunchul Park

Programming Systems Lab

Intel Labs

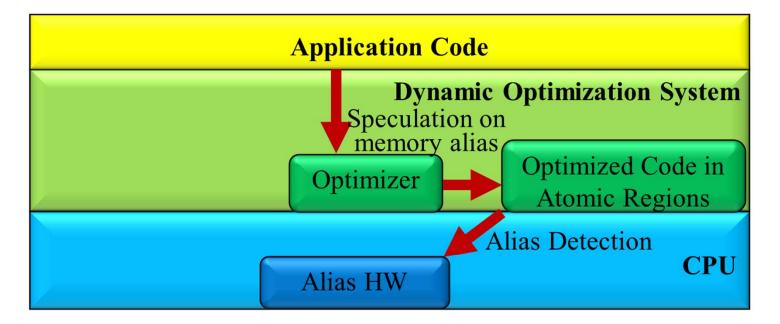

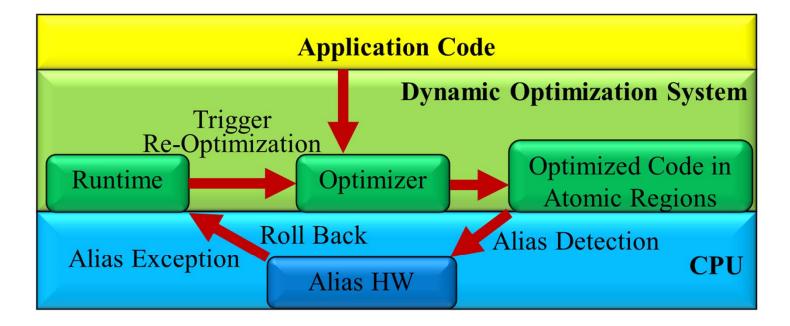

# Dynamic Optimization with Hardware Alias Detection

# Dynamic Optimization with Hardware Alias Detection

$$M_0$$

: st [r0] = ...  $M_1$ : ... = Id [r1]

$$M_0$$

: st  $[r0+4] = ...$

$M_1$ : ... = Id  $[r1]$

$M_2$ : st  $[r0] = ...$

$M_3$ : ... = Id  $[r2]$

A memory operation (i.e.  $M_0$ ) may need to check multiple alias registers (i.e. AR0, AR1)

- A memory operation (i.e. M<sub>0</sub>) may need to check multiple alias registers (i.e. AR0, AR1)

- Transmeta Efficeon uses a bitmask in the instruction to specify the individual alias registers to be checked

- cannot scale up to a large number of alias registers

- A memory operation (i.e. M<sub>0</sub>) may need to check multiple alias registers (i.e. AR0, AR1)

- Transmeta Efficeon uses a bitmask in the instruction to specify the individual alias registers to be checked

- cannot scale up to a large number of alias registers

- Itanium Advanced Load Address Table (ALAT) checks all alias registers set by previous advanced loads

- may lead to false positive (i.e. M<sub>2</sub> checks M<sub>1</sub>)

- can not check alias between stores

# **Background 2: Order-Based Alias Detection**

```

M_0: st [r0+4] = ...

M_1: ... = Id [r1]

M_2: st [r0] = ...

M_3: ... = Id [r2]

```

# **Background 2: Order-Based Alias Detection**

```

M_3: ... = Id [r2] , order 3

M_1: ... = Id [r1] , order 1

M_2: st [r0] = ... , order 2

M_0: st [r0+4] = ... , order 0

```

# **Background 2: Order-Based Alias Detection**

# Background 2: Order-Based Alias Detection

# Background 2: Order-Based Alias Detection

- Adopted in out-of-order CPU (Id/st queue) for HW speculation

- Detect all the aliases between reordered memory operations without any false positive

- HW automatically identifies loads to prevent alias check between them (E.g. M<sub>1</sub> does not check AR3)

#### **Order-Based Alias Detection Issues**

- Do not leverage compiler analysis for efficient alias register usage

- 4 alias registers are used

- M<sub>0</sub> does not need to check M<sub>2</sub>

#### **Order-Based Alias Detection Issues**

- Do not leverage compiler analysis for efficient alias register usage

- 4 alias registers are used

- M<sub>0</sub> does not need to check M<sub>2</sub>

- Only consider memory reordering, but not general optimizations such as load/store elimination

- May need alias check between non-reordered memory operations

# Check Between Non-Reordered Memory Operations

#### **Motivation**

#### **SW-Managed Alias Register File**

- SW Speculation on In-Order CPU

- Itanium False Positive Issue

- Transmeta Scalability Issue

#### **HW-Managed Alias Register Queue**

- HW Speculation on Out-of-Order CPU

- Efficiency Issue

- Generalization Issue

# SMARQ: SW-Managed Alias Register Queue

- Novel architecture features and compiler algorithms

- Solve all the issues in previous works

```

M_0: st [r0+4] = ...

M_1: ... = Id [r1]

M_2: st [r0] = ...

M_3: ... = Id [r2]

```

$$M_3$$

: ... = Id [r2]

$M_1$ : ... = Id [r1]

$M_2$ : st [r0] = ...

$M_0$ : st [r0+4] = ...

- · Compiler analysis to derive necessary alias checking for the optimization

- Check-constraint A → B: A needs to check B for alias

```

M_3: ... = Id [r2] , P

M_1: ... = Id [r1] , P

M_2: st [r0] = ... , C

M_0: st [r0+4] = ... , C

```

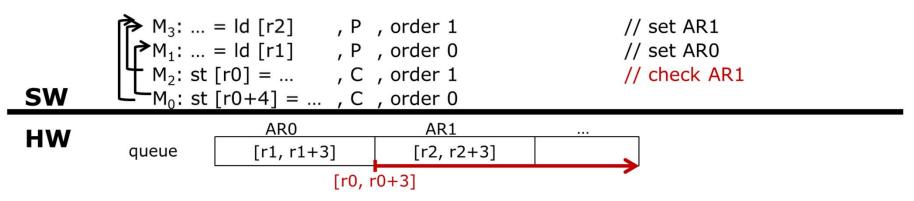

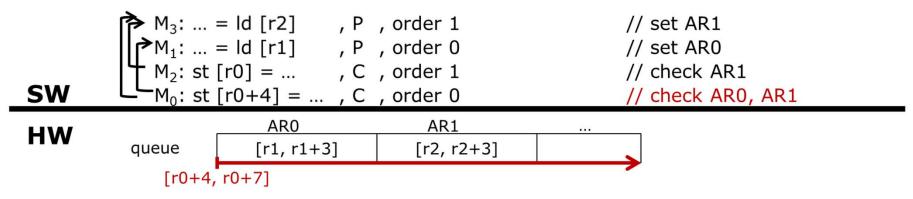

- Compiler analysis to derive necessary alias checking for the optimization

- Check-constraint A → B: A needs to check B for alias

- Leverage architecture features for efficient management of the alias register queue

- P bit for setting alias register and a C bit for checking alias registers (may have both)

```

M_3: ... = Id [r2] , P , order 1

M_1: ... = Id [r1] , P , order 0

M_2: st [r0] = ... , C , order 1

M_0: st [r0+4] = ... , C , order 0

```

- Compiler analysis to derive necessary alias checking for the optimization

- Check-constraint A → B: A needs to check B for alias

- Leverage architecture features for efficient management of the alias register queue

- P bit for setting alias register and a C bit for checking alias registers (may have both)

- Alias register order allocation respecting check-constraints

- A  $\rightarrow$  B  $\Rightarrow$  order(A) <= order(B)

- The alias register order for different instructions with P bit must be different

- Compiler analysis to derive necessary alias checking for the optimization

- Check-constraint A → B: A needs to check B for alias

- Leverage architecture features for efficient management of the alias register queue

- P bit for setting alias register and a C bit for checking alias registers (may have both)

- Alias register order allocation respecting check-constraints

- $A \rightarrow B \Rightarrow order(A) <= order(B)$

- The alias register order for different instructions with P bit must be different

- Compiler analysis to derive necessary alias checking for the optimization

- Check-constraint A → B: A needs to check B for alias

- Leverage architecture features for efficient management of the alias register queue

- P bit for setting alias register and a C bit for checking alias registers (may have both)

- Alias register order allocation respecting check-constraints

- $A \rightarrow B \Rightarrow order(A) <= order(B)$

- The alias register order for different instructions with P bit must be different

#### **Prevent False Positive**

- Alias register order respecting check-constraint may cause false positive in alias checking

- No restriction on the alias register order between  $\rm M_1$  and  $\rm M_2$  and Incorrect order between them will cause  $\rm M_2$  to check  $\rm M_1$

#### **Prevent False Positive**

- Alias register order respecting check-constraint may cause false positive in alias checking

- No restriction on the alias register order between  $\rm M_1$  and  $\rm M_2$  and Incorrect order between them will cause  $\rm M_2$  to check  $\rm M_1$

- Anti-constraint A -->B: A should not be checked by B

- $-A-->B \Rightarrow order(A) < order(B)$

# **Advanced SMARQ Features**

- Alias register rotation\*

- HW organize the alias registers as a circular queue rotated through a base alias register pointer

- SW rotate the alias register queue to release dead alias register, just like the release of ld/st queue entry in out-of-order CPU

- Handle order cycles\*

- The alias register order respecting all the check-constraints and anti-constraints may contain cycles

- No alias register order can detect all the aliases without any false positive

- New architecture alias-register-move feature to break all the cycles

- Prevent alias register overflow\*

- It is hard to support alias register spill

- Allocate alias register during list scheduling so that if alias register may overflow, schedule instruction to respect all aliases without using new alias registers

#### \* See details in the paper

# **Experiment Setup**

dynamic optimization framework translates and optimizes x86 binary codes into code running on an internal VLIW CPU modeled by a cycle-accurate

| Architecture Features | Parameter                                                        |

|-----------------------|------------------------------------------------------------------|

| 8-wide VLIW           | 2 INT units, 2 FP units, 2 MEM unit, 1 BRANCH unit, 1 ALIAS unit |

| L1 I-Cache            | 4-way 256KB                                                      |

| L1 D-Cache            | 4-way 64KB, HW prefetch                                          |

| L2 Cache              | 8-way 2MB, 8 cycle latency,<br>HW perfetch                       |

| L3 Cache              | 8-way 8MB, 25 cycle latency                                      |

| Memory                | 1GB, 104 cycle latency                                           |

| Alias Register Queue  | 64 entries                                                       |

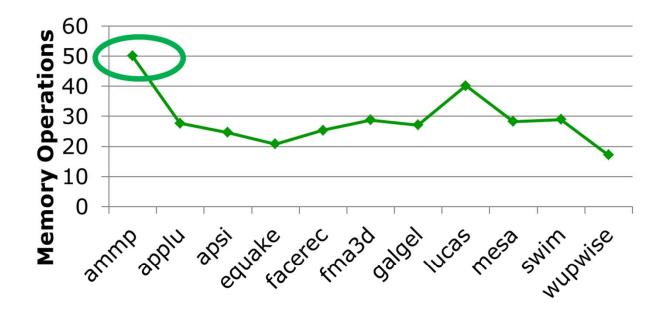

# **Average Region Size**

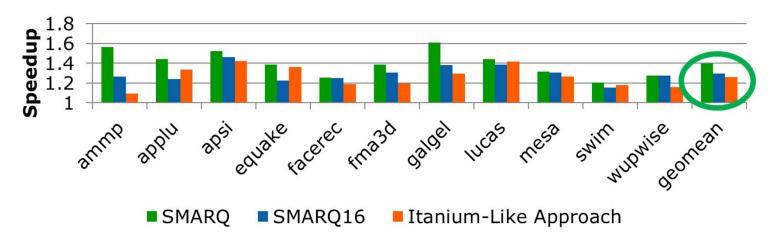

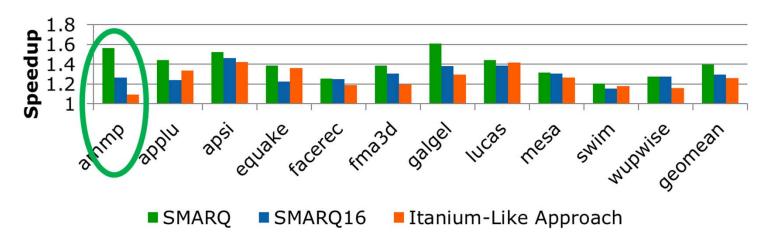

# **Speedup with Different Alias Detection**

- · Baseline: no HW alias detection

- SMARQ: 39% speedup on average

- SMARQ16: restrict alias register queue to 16 entries

- 29% speedup

- Itanium-like approach: non ordered alias detection (with false positives)

- 26% speedup

# **Speedup with Different Alias Detection**

- · Baseline: no HW alias detection

- SMARQ: 39% speedup on average

- SMARQ16: restrict alias register queue to 16 entries

- 29% speedup

- Itanium-like approach: non ordered alias detection (with false positives)

- 26% speedup

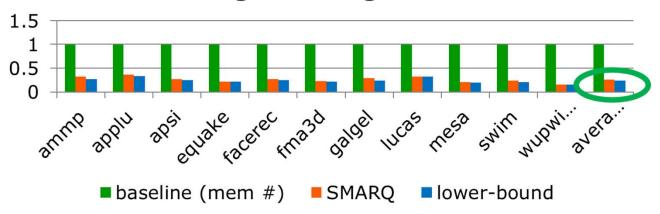

# **Alias Register Working Set**

#### **Average Working Set Size**

- · Baseline: allocate each memory operation a unique alias register in their program order

- SMARQ: reduce the average alias register working set by 74%.

- Lower bound: maximum number of overlapped alias register live-ranges

- SMARQ achieves alias register working set size close to the lower bound.

#### **Conclusions**

- We identify in details the issues in all the previous works on alias registers

- We proposed SMARQ, a software managed alias register queue to solve all the issues in previous works

- improve the overall performance by 39% as compared to the optimization without alias register

- reduce the alias register working set by 74%